News: June 2022

Project F news is back! It’s been a while, so this edition covers the first half of 2022. There are six new blog posts to cover as well as plans for the next few months. News will now be quarterly, with the next update in late September 2022.

New Posts

Beginning FPGA Graphics

Beginning FPGA Graphics is a completely rewritten introduction to FPGA Graphics. I’ve added new diagrams, improved explanations, and included friendly examples with flags. I’ve also introduced Verilog/SDL simulations, which provide a great way to test designs and allow those without a dev board to get started with hardware design.

If you’re looking to start designing graphics hardware or want a project to take you beyond blinking LEDs, this post is for you.

Racing the Beam

Racing the Beam is a new post for 2022. It includes five simple demos that build on what you learned in Beginning FPGA Graphics. The demos are raster bars, hitomezashi stitch pattern, basic bitmaps, colour cycling, and animated squares.

FPGA Pong

FPGA Pong is a fresh version of Pong written in Verilog. It shows you how to build a game entirely in logic, including AI player, collision detection, and scoring. I provide a finished design and then take you through it step-by-step. Building a game from scratch isn’t as hard as you might imagine.

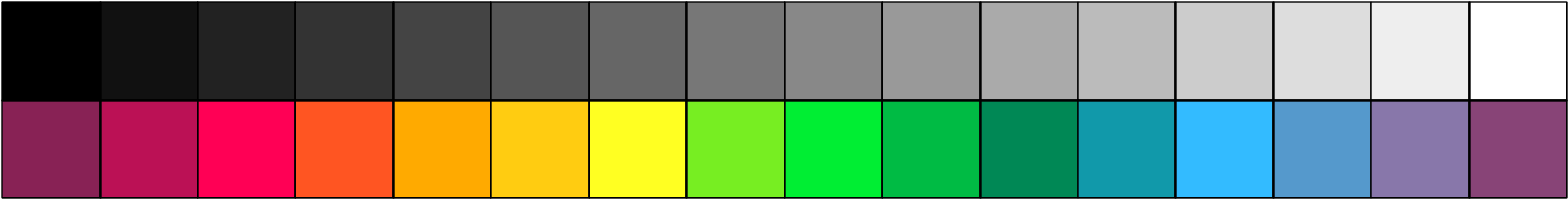

Display Signals

Display Signals introduces a more robust and capable display signal generator. Working with signed coordinates, we can load graphics and draw beyond the edge of the screen with ease. We also cover palettes and a colour lookup table (CLUT) for rich coloured graphics using minimal resources.

Hardware Sprites

![]()

Hardware Sprites introduces brand-new sprite designs. Starting with small monochrome sprites, we develop larger and more colourful sprites using a colour lookup table. By the end of this post, you’ll be able to define your own sprite graphics and effortlessly move them around the screen. More advanced sprite designs will follow later in 2022.

Simple Clock Domain Crossing

Sometimes you need to send a single pulse from one clock domain to another. This is a simple case of clock domain crossing or CDC. clock/xd shows you how to use the xd module from the Project F Library to handle such situations simply and safely.

What’s Next?

Real Numbers

The next part of my series on mathematics and algorithms will cover real numbers, focusing on fixed-point representations. If time permits, I’d also like to expand my coverage of division in Verilog.

Framebuffer

I have an improved framebuffer to roll out to the graphics series. This new design separates display output from drawing for a simpler, more flexible design. With this new design, I’ll finally be able to support double buffering properly on iCEBreaker (iCE40UP).

Thank You, Sponsors!

I’d like to thank my sponsors for supporting my work on Project F: Doug Johnson, Paul Sajna, Juri Tsirihhov, STjurny, ketmonkey, gymmy1, Adrian Scripcă, and John W. Terrell.

If you like what I do, consider joining them and sponsoring me on GitHub. I love FPGAs and want to help more people discover and use them in their projects.

Read the September 2022 news or see the news archive.