News: June 2021

Project F news is your monthly update on the project, with tasty tips and links thrown in. Last month’s issue was well received, so I’m continuing with the experiment. June wasn’t the easiest of months, with a stint of COVID self-isolation1, but I’m happy to have written about Verilator and SDL. If you have any comments, find me on Mastodon @WillFlux@mastodon.social, or open an issue on GitHub.

Read the July 2021 news or see the news archive.

Blog

June saw one new blog post: Verilog Simulation with Verilator and SDL.

Simulation of graphical hardware is one of those things that seems intimidating, but Verilator and SDL make it straightforward. We take the simple designs from Intro to FPGA Graphics, add a dash of C++, and produce animated simulations with minimal effort. I have begun pushing Verilog simulations to the git repo; you can see the first set for Intro to FPGA Graphics (GitHub).

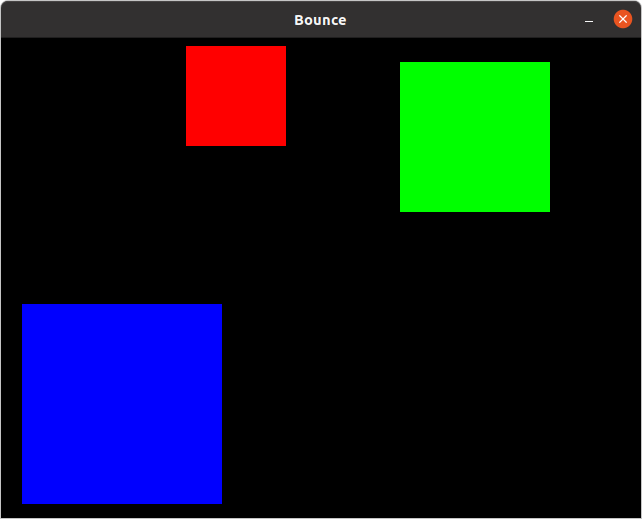

The following screenshot shows a Verilator simulation of Top Bounce running on Linux:

Videos

I did my first ever interview this month. Matthew Venn and I discussed Project F, graphics, simulation, and tradeoffs in hardware design. You can watch it on YouTube or listen to the podcast.

If you’re interested in designing your own ASIC, check out the Zero to ASIC Course. To hear about future Project F videos, please subscribe to my YouTube Channel.

Quick Updates

I make many small improvements and corrections every month.

Here are some examples from June:

- Better test benches for Square Root in Verilog

- New explanations of combinational and sequential logic in Hello Arty Part 2

- Inspirational projects to show what’s possible with FPGA graphics

- Explained nproc in Building iCE40 FPGA Toolchain on Linux

Bits & Tips

iCE40UP SPRAM

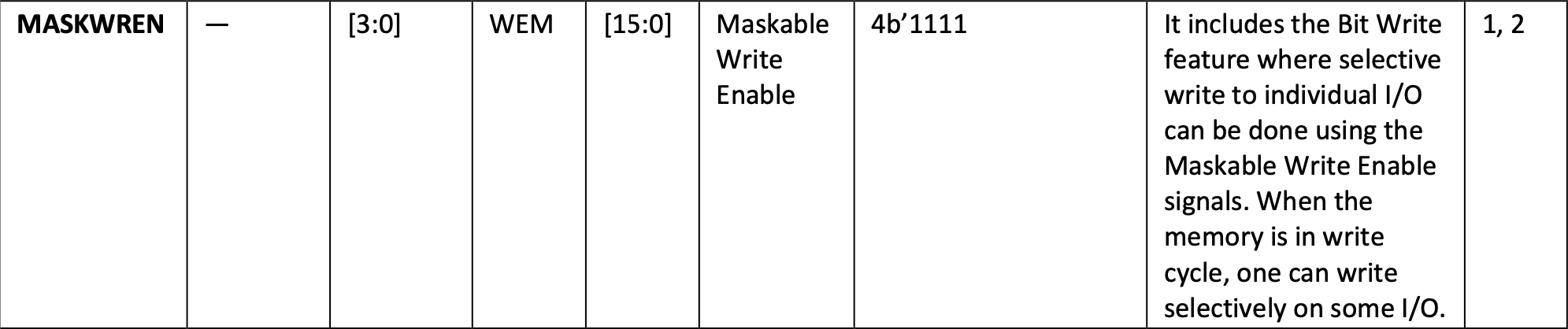

I was reading the iCE40UP SPRAM datasheet when I spotted something I’d overlooked: nibble (4-bit) write.

Nibbles are more common than you might imagine, for example, when dealing with QSPI. Perhaps unsurprisingly, my main interest is graphical: a 320x180 x 4-bit framebuffer fits beautifully into a 256Kb SPRAM. Look out for an update to framebuffers soon; in the meantime you can search for MASKWREN in the SPRAM datasheet.

CXXRTL

This month I started learning about CXXRTL. CXXRTL is a Yosys simulation backend that turns your Verilog modules into C++ classes. Tom Verbeure has an informative introduction: CXXRTL, a Yosys Simulation Backend, and Konrad Beckmann provides a great example of graphic simulation with CXXRTL (Twitter).

Interesting Links

FPGA and RISC-V links that caught my eye:

- Software support for custom RISC-V instructions (Twitter)

- Taking delivery of a VCU128 FPGA board with a million LUTs (Twitter)

- Silice Verilator graphical simulation framework (GitHub)

- Soft CPU Performance on modern FPGAs (Google Doc)

- Intel Might Purchase SiFive for $2 Billion (YouTube)

For more great links, try Recommended FPGA Sites.

And Finally

After dealing with tiny PCB components, it’s nice to look at something more substantial. Tim Hunkin’s CHAIN - The Secret Life of Components is the first part of an excellent series on practical design, covering LEDs, switches, springs, connectors, and even glue.

Read the July 2021 news or see the news archive.

-

I was in contact with someone who tested positive. I tested negative, but still had to isolate. ↩︎