News: July 2021

Project F news is your monthly update on the FPGA project, with tasty tips and links from other developers thrown in. This month, iCE40 SPRAM takes centre stage, filled triangles add graphical goodness, we learn that Linux will fit on an iCEBreaker, and discover FPGAs on Mars. If you have any comments, share your thoughts with @WillFlux@mastodon.social or find me on 1BitSquared Discord.

Read the August 2021 news or see the news archive.

SPRAM on iCE40 FPGA

There was one new blog post this month: SPRAM on iCE40 FPGA. SPRAM is one of the best features of the iCE40UP FPGAs, providing 1 Mb of ram organised as four 256 Kb (16K x 16-bits) blocks. While not as versatile as block ram, it’s pretty generous for such a small FPGA.

I’ve been trying to bring my iCEBreaker graphics designs up to feature parity with the Arty (Xilinx 7 series). The biggest obstacle has been the iCE40UP’s lack of block ram (120 Kb total), which I have been using as a framebuffer. A 256 Kb SPRAM block is ideal for a 320x180 16-colour framebuffer, leaving other blocks free for soft CPU etc. However, SPRAM only has one port (obviously), which required some tweaks to my framebuffer designs. I plan to roll out new iCEBreaker designs with SPRAM during August; keep an eye on Lines and Triangles and 2D Shapes.

Filled Triangles

A new filled-triangle module rounded out my drawing modules in July. You can find the design in the Verilog library on GitHub: draw_triangle_fill.sv.

There are several approaches to drawing filled triangles, but I opted to build on the existing Bresenham’s line triangle outline. This simple approach avoids multiplication and can still draw over 1 million medium-sized triangles at 100 MHz.

Read more in 2D Shapes and check out this rendering of a cube using six triangles:

Faster Verilator SDL

In June, I published a quick guide to Verilog Simulation with Verilator and SDL. My design wasn’t especially fast, as it polled for SDL events every clock. Dave Dribin submitted a pull request that improved the performance and added framerate reporting. The blog has been updated with the new design, and you can find the latest source and instructions in the GitHub repo.

FPGA Resources

I added several new entries to my recommended FPGA resources, including YouTube channels. Ping @WillFlux@mastodon.social if you have any additional suggestions.

Interesting Links

FPGA and RISC-V links that caught my eye:

- Sylvain Munaut gets Linux running on iCEBreaker (YouTube)

- Bruno Levy puts open-source tools for Xilinx FPGAs to the test (Twitter)

- Olof Kindgren predicts SERV LUT usage will reach zero during 2023 (Twitter)

- First new VAX in 30 years? On a Spartan-3 FPGA no less! (NetBSD ML)

- Ian Cutress takes delivery of teeny tiny FPGAs (Twitter)

For more great links, try Recommended FPGA Sites.

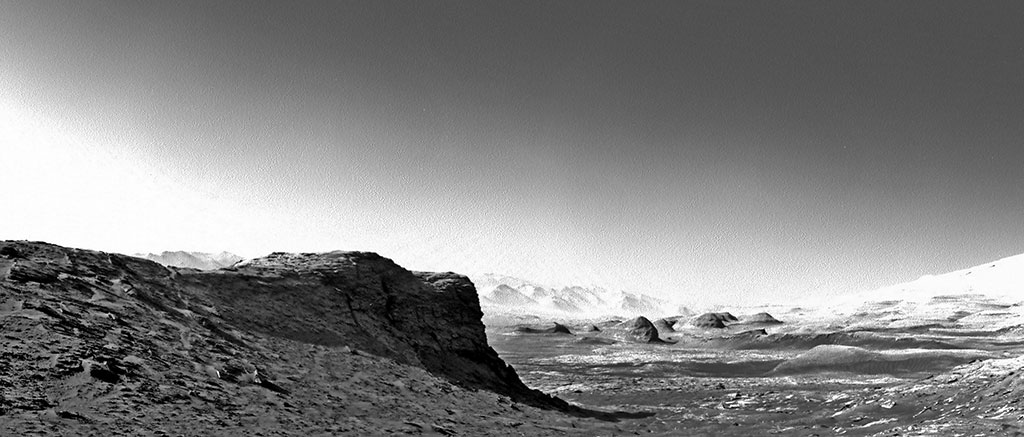

And Finally: A View from Another World

Perseverance Rover Lands on Mars with FPGAs On Board (Xilinx blog from February 2021).

Image Credit: NASA/JPL-Caltech/S Atkinson. Learn more at mars.nasa.gov.

Thanks to @mars_stu for bringing this photo to my attention.

Read the August 2021 news or see the news archive.