News: April 2023

Welcome to the latest Project F news covering the first part of 2023. In this edition, we sail the sea of chaos, round out division, automate Vivado with Tcl, and uncover openFPGALoader and cocotb.

This is the last news installment in this series.

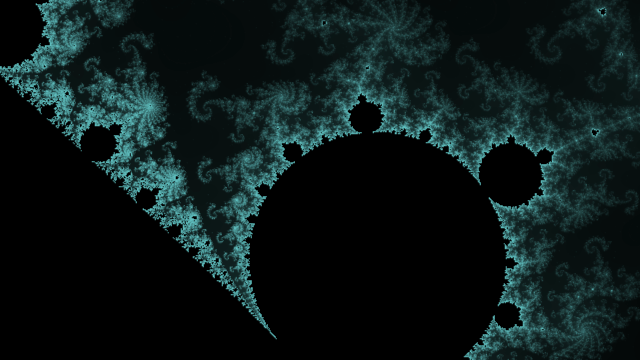

Fractal FPGA

I’ve been experimenting with fractals to test my maths designs. In March, I posted Mandelbrot using fixed-point maths and a small framebuffer to render the Mandelbrot set.

The multiplication module could use some optimisation, and we only consider one pixel at a time, but it’s still a fun little demo to try on your dev board (or in simulation).

Mandelbrot Verilog source and build instructions (GitHub)

Divided We Stand

In January, I designed a new fixed-point division module with Gaussian rounding. Better rounding is important for many algorithms and adds negligible overhead to a simple division module. Read more in Division in Verilog.

I used cocotb for the first time in testing my new module. cocotb is a Python-based testing tool that works with existing simulators, such as Icarus Verilog. I found cocotb to be a productive testing tool, if a little frustrating at first. I intend to write about cocotb when I have more experience with it.

Here’s an example of a division test:

@cocotb.test()

async def round_8(dut): # negative

"""Test -7.0625/2"""

await test_dut_divide(dut=dut, a=-7.0625, b=2)

And the test output:

367.02ns INFO cocotb.regression running round_8 (17/32)

Test -7.0625/2

389.02ns INFO cocotb.div dut a: 110001111

389.02ns INFO cocotb.div dut b: 000100000

389.02ns INFO cocotb.div dut val: 111001000

389.02ns INFO cocotb.div -3.5

389.02ns INFO cocotb.div model val: 111100.1000

389.02ns INFO cocotb.div -3.5

390.02ns INFO cocotb.regression round_8 passed

You can see the full source of the division test in git: lib/maths/test/div.py

Tickling Vivado

Vivado is de rigour for working with Xilinx FPGAs but can be an unforgiving beast. Vivado is built around Tcl scripting, which deterred me from automating things when I first got an Arty board in 2018. However, experience has taught me that simple Tcl scripting is helpful and not difficult. In my latest blog post, I aim to show you how straightforward a Tcl script can be: Vivado Tcl Build Script

Bits and Pieces

Project F Discussion Forum

Several people requested I open a Project F discussion forum on GitHub, which I did in February. Pop on over with your question or suggestion on any Project F design. You can also find me on 1BitSquared Discord if that’s more your thing.

Better Blanking

One fruitful discussion was Improving the Colour Test code for analog VGA that led me to improve the video blanking design:

// display colour: paint colour but black in blanking interval

logic [CHANW-1:0] display_r, display_g, display_b;

always_comb {display_r, display_g, display_b} = (de) ? {paint_r, paint_g, paint_b} : 0;

I’d previously had different, ad-hoc logic to cover colour in the blanking interval, which allowed annoying bugs to creep in. The new design ensures the colour is always black in the blanking interval.

openFPGALoader

This year, I’ve started using openFPGALoader to program my FPGA dev boards. openFPGALoader supports a wide range of FPGAs, dev boards, and cables and is available in the OSS CAD Suite.

I’ve liked building a Vivado project on a remote machine and programming a Xilinx dev board locally with openFPGALoader, even from a Mac.

New Blog Design

As you’ve probably noticed, the Project F blog has a clean new look. Overly-thin body text is out; chunkier design is in. Plus, there’s better mobile scaling and dark mode for those late-night design sessions. The blog remains free from adverts and cookies.

Outside Interests: Revision

The Revision demo party was back at E-Werk for 2023.

My favourite Amiga prods:

- Electric Lifeforms [YouTube] (Amiga 64K Intro)

- Neocolora by Darkage & Lemon [YouTube] (Amiga Demo)

- Cycle-Op by Oxygene [YouTube] (Amiga Demo)

YouTube playlist for all the compos: Revision 2023 - Compos

I didn’t enter an FPGA demo this year, but maybe I’ll be back in in 2024? ;)

What’s Next?

I’ll continue improving my existing designs and blog posts throughout 2023 but plan to focus on two new areas: video capture and a new FPGA series.

Video Capture

Thanks to my lovely sponsors, I have a shiny new Blackmagic UltraStudio Recorder 3G. This small box lets me capture smooth, high-quality DVI and HDMI output from FPGA dev boards.

The Blackmagic doesn’t support 640x480, which has given me the kick I needed to add 1280x720 versions of the FPGA graphics series. I’ve merged 5 of 9 designs for Nexys Video in git and will finish the remainder soon. Once the whole series is in place, I’ll upload videos to YouTube.

Video is one of the best ways to explain hardware design, so I plan to make video capture a regular part of my designs in future. Subscribe to the Project F YouTube Channel and stay tuned.

New FPGA Series

I’ve started work on a new FPGA series but am not ready to reveal it yet. Rest assured, the new series will stick to the Project F philosophy of accessible open-source FPGA designs.

Why the new approach? With the graphics and maths series, I’ve completely revised the designs and blog posts several times. For this next series, I plan to complete an initial version of the designs before going public. That way, I can take a more holistic approach to the designs and blog writing.

Thank You, Sponsors!

Thank you to my sponsors for supporting my work on Project F: David C. Norris, Didier Malenfan, Michael Doornbos, kromych, LaDirth, matt venn, Paul Sajna, STjurny, and those who wish to remain anonymous.

If you like what I do, consider joining them and sponsoring me on GitHub. I love FPGAs and want to help more people discover and use them in their projects.

This is the latest news post, but you can always browse the news archive.